# Journal of Applied Research in Electrical Engineering

E-ISSN: 2783-2864 P-ISSN: 2717-414X Homepage: https://jaree.scu.ac.ir/

## Research Article

Electrical and Electronics

# A Feedforward Active Gate Voltage Control Method for SiC MOSFET Driving

Hamidreza Ghorbani\* , and Jose Luis Romeral Martinez

MCIA-Motion Control and Industrial Applications, Universitat Politècnica de Catalunya, Barcelona, Spain

\* Corresponding Author: hamidreza.ghorbani@upc.edu

Abstract: A new active gate drive for Silicon carbide (SiC) metal-oxide-semiconductor field-effect transistor (MOSFET) is proposed in this paper. The SiC MOSFET as an attractive replacement for insulated gate bipolar transistor (IGBT) has been regarded in many high power density converters. The proposed driver is based on a feedforward control method. This simple analog gate driver (GD) improves switching transient with minimum undesirable effect on the efficiency. This paper involves the entire switching condition (turn on/off), and the GD is applied to the SiC base technology of MOSFET. To evaluate the performance of the proposed GD, it will be compared with a conventional gate driver. The presented GD is validated by experimental tests. All the evaluations are carried out in a hard switching condition and at high-frequency operation.

Keywords: Active gate driver (AGD), SiC MOSFET, switching condition, feedforward control.

## **Article history**

Received 08 January 2022; Revised 09 January 2023; Accepted 19 February 2023; Published online 29 March 2023.

© 2023 Published by Shahid Chamran University of Ahvaz & Iranian Association of Electrical and Electronics Engineers (IAEEE)

#### How to cite this article

H. Ghorbani, and J. L. R. Martinez, "A feedforward active gate voltage control method for SiC MOSFET driving," *J. Appl. Res. Electr. Eng.*, vol. 2, no. 1, pp. 87-94, 2023. DOI: 10.22055/jaree.2023.39698.1045

## 1. Introduction

Conventional IGBTs are conventional switches in the structure of the power converters. However, because of some weak points such as operation in low-speed switching and low-temperature condition, the studies have been driven to silicon carbide (SiC) technology. SiC technology in power switches has emerged as a serious alternative to overcome the disadvantages of Si-switches. SiC device has some advantages such as higher operating frequency and temperature and lower on-resistance due to its bandgap and unipolar nature [1-2]. Moreover, due to its fast switching behaviour and shorter switching time, a better switching efficiency can be expected. In order to gain as efficiently as possible, engineers try to switch as fast as possible. However, the high speed switching in SiC MOSFETs increases the electromagnetic interference (EMI) emission. Therefore, the existing trade-off between efficiency improvement and EMI reduction through switching control brings a challenge in the gate driver designing. In addition, the SiC MOSFET normally has large input capacitance and higher threshold voltage, therefore more complex and sensitive driver is needed [3].

Several gate drivers (GDs) have been presented to improve the mentioned trade-off between fast switching and EMI [4-8]. However, most of them have been assigned to Si-

MOSFET or IGBT applications. Also, mainly they can be categorized in the closed-loop controller. Typically such controllers are effective and comprehensive for GDs, but in general, they increase the complexity of the GD's circuit. Therefore, some of the presented approaches are not attractive solutions for industrial. Moreover, in high-frequency operation rates, when SiC MOSFET is under hard switching condition; the advent of EMI problem is possible. Hence, designing proper GD for SiC MOSFETs has significant importance.

## 1.1. Overview of Gate Drivers for Power Devices

In order to enhance power density in switch-mode applications, operation at high switching frequency is necessary due to reducing the size of its passive component as well as it reduces the size of the heatsink. Thereby, the operation of IGBT is limited at the low switching frequencies ( $<20 \, \mathrm{kHz}$ ) [9]. However, in high speed switches the transition rates of current and voltage (di/dt and dv/dt respectively) get higher values. Also, parasitic inductance results some problematic oscillations and overshoots in current and voltage waveforms [10]. Changing the gate resistor  $R_g$  is known as a conventional solution [11-12]. Although the overshoot suppression can be achieved by high  $R_g$  value. However, the id and  $V_{ds}$  both get lower slopes which cause to increase switching times. As a result, the increased  $R_g$

sacrifices additional switching losses. Another conventional driving technique is the use of an external gate-source capacitance ( $C_{gs}$ ) in the GD circuit [13]. However, it increases the input capacitance ( $C_{ies}$ ). This technique is used for IGBT's gate drivers due to roughly better efficiency (compared to the method of solely  $R_g$  increasing). Nevertheless, the gate capacitance is a parasitic element which potentially provokes transients and it can create some parasitic problems such as imposing the stress and crosstalk problem [14-15]. As a result, this may not be a favorable solution for SiC MOSFET applications which typically has large input capacitance. To improve the existing trade-off between switching loss, stress and EMI; diverse approaches have been proposed such as applying snubber circuits in Si and SiC devices [16-17] active gate voltage controlling [18] active gate current driving [19] resonant gate drivers [16, 20], etc. All mentioned techniques could be used for driving SiC MOSFETs. Although, these GDs can minimize stress from the power device, however, these deal with more complexity or more cost and more switching losses. The control of GDs is not the single possible way for EMI reduction, rather with using a better design of PCB layout the parasitic (stray) inductances can be reduced, and consequently we will have less EMI problems.

## 1.2. SiC MOSFET Gate Drivers

The SiC MOSFETs are widely employed in power converters due to its advantages. This switching technology inherently has lower trans-conductance compared to Si-MOSFETs or IGBTs. Thus, higher orders of gate-source voltage are required for switching-on. Also, the gate-source voltage pulse is commonly asymmetrical. Therefore, different values of Rg should be used in their GDs [21]. Conventionally, two different gate resistance is used in the drive circuit for controlling each turn path. This common driver controls both turn-on and turn-off paths separately. A gate boost circuit was introduced for SiC MOSFET driving in [22] which had reduced the switching losses, however, the transient and overshoots had not been reduced. The same technique is presented in [23] as well. Many studies for controlling di/dt and dv/dt transition by closed-loop control method have been reported [23-26]. Such controllers have been allocated to guarantee the safe operation of MOS-gate switches under different and variable loads. However, they increase the complexity of the driver's circuit.

According to the presented overview, most of the offered approached are related to efficiency improvement and for solving some other issues such as EMI reduction, overshoot suppression, stability improvement etc. mainly the presented solutions have fallen in the complex closed-loop GD controllers. This paper presents a simple control method for driving SiC MOSFETs. The control concept is based on a feed-forward controller. The effective performance of the controller beside its simple structure is the main advantage of this GD. The purpose is the switching transient improvement with a minimum undesirable effect on efficiency. In the next section, the operation of SiC MOSFET and the principles of new GD are presented.

#### 2. ACTIVE GATE DRIVER

#### 2.1. Principles of Proposed Controller

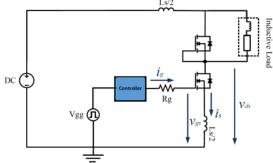

The test circuit is represented in Fig. 1. The controller is applied into the gate circuit. The profile of Vgg voltage signal is changed by the controller and it is delivered to the gate port of MOSFET. In order to test in a hard-switching condition, the load is highly inductive.

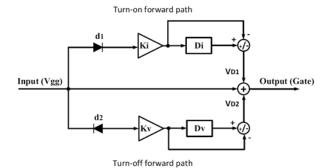

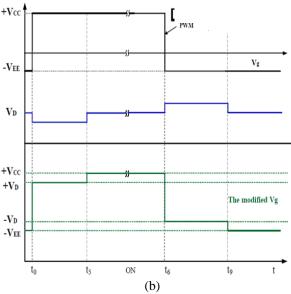

The schematic of the proposed controller is depicted in Fig. 2. Since the SiC MOSFET meets several intervals during the switching conditions, controller changes the profile of gate signal during MOSFET's active region (Fig. 3a shows these intervals). The modification process of gate signal has been demonstrated in Fig. 3b. The turn-on is initiated at  $t_0$ , and step voltage (from  $-V_{EE}$  to  $+V_{CC}$ ) is applied to the gate. As shown in Fig. 2, each switching state is separated from the other by diodes for individual controlling. The positive side of voltage signal is driven by  $d_1$  and the  $d_2$  conducts its negative for turn-on and turn-off controlling respectively. Both control paths have same structure and operate based on same concept.

However, the required parameters should be defined according to each switching condition. In both cases, the controller gets a step voltage value ( $\Delta V_g$ ) according to (1) from the input. Depending on the suppression rate of overshoot at each swathing state, a portion of the input value is given to the corresponding control path.  $K_i$  and  $K_v$  represent these coefficients for turn-on and turn-off controlling respectively.

In each switching condition, weakened signal with a negative coefficient is summed with the same positive signal

Fig. 1: Schematic of test circuit.

**Fig. 2:** Block diagram of the proposed feedforward controller.

**Fig. 3:** (a) The transient behavior of MOSFET switching, and (b) controller performance for Vg modification.

that has a delay. These delays are created by blocks  $D_i$  and  $D_v$ . The applied  $D_i$  delay covers whole turn-on  $(t_0 < t < t_5)$  and  $D_v$  covers turn-off  $(t_6 < t < t_9)$  intervals. The resultant voltage signal is called  $V_D$  here. Finally, the original  $V_{gg}$  signal after summing with  $V_{DI}$  and  $V_{D2}$  results modified  $V_g$  signal which is applied on gate port for driving MOSFET. The modified  $V_g$  affects to the current transient while turn-on condition and as well as to the dynamic of voltage during turn-off condition.

$$\Delta V_q = V_{cc} - V_{EE} \tag{1}$$

According to what has been presented in [27], with a little approximation the current and voltage transitions may be defined as (2) and (3), which both depend on a different

voltage value between  $V_g(+/-)$  to  $V_{gs}(th)$ . This differential voltage value affects to the injected gate current  $i_g$  in each switching state. Thereby, the used technique can be effective to control of both current and voltage transitions.

$$\frac{d_{id}}{dt} = g_m \cdot \frac{V_{cc} - V_{gs}(th) - \frac{id}{2 \cdot g_m}}{C_{iss} \cdot Rg}$$

(2)

$$\frac{dv_{DS}}{dt} = \frac{V_{EE} + V_{gs(plateau)}}{C_{gd} \cdot R_g}$$

(3)

In (2),  $g_m$  is the trans-conductance and  $C_{iss} = C_{gs} + C_{gd}$  is the input capacitance of the SiC MOSFET. All details about the switching process of the MOSFET is fairly well demonstrated in [10]. Here, we present the performance of the new gate driver for controlling  $di_d/dt$  and  $dv_{ds}/dt$  rates.

#### 2.2. Parameters and Limitations

For tuning the controller in each switching state two parameters are necessary.  $K_i$  coefficient and the  $D_i$  delay for turn-on and  $K_{\nu}$  coefficient and the  $D_{\nu}$  delay for turn-off. In the case of delays, these parameters can be determined based on application note or experimental observations. As already mentioned, the delay time must cover whole active region times. Because of the time difference between switching on and off, two individual delays have been considered for corresponding states as shown in Fig. 2. It should be noted that the margin determination for delays is not a delicate factor. Because after finishing  $D_i$  or  $D_v$  delay, the modified  $V_g$ returns to its original value when MOSFET is in the saturation (steady state) region. For this reason, the delay time could be defined much longer than switching time. The K coefficient determines  $V_D$  voltage value (see Fig. 3b and (5)) or in other word, it determines the  $\Delta V_g$  voltage value while controlling time. As a result, the injected gate current and then switching transient will get effect by that.  $V_D$  is the reduced voltage level during turn on/off. Since the SiC MOSFETs driving is asymmetric and the absolute value of  $V_{EE}$  is smaller than  $V_{CC}$ , thus the change domain of the  $V_{gg}$  for each switching state must be determined individually. For turn-on condition  $K_i$ coefficient can be obtained by the following equations.

$$V_{as}, th < \sigma_1 < V_{cc} \tag{4}$$

$$V_D^+ = V_{cc} - \sigma_1 \tag{5}$$

$$\Delta V_{m1} = V_D^+ - V_{EE} \tag{6}$$

$$K_i = 1 - \left(\frac{\Delta V m 1}{\Delta V_q}\right) \tag{7}$$

As well as for turn-off condition,  $K_{\nu}$  coefficient can be defined as:

$$V_{EE} < \sigma_2 < 0 \tag{8}$$

$$V_D^- = V_{EE} - \sigma_2 \tag{9}$$

$$\Delta V_{m2} = V_{cc} - V_D^- \tag{10}$$

$$K_{v} = 1 - \left(\frac{\Delta V_{m2}}{\Delta V_{q}}\right) \tag{11}$$

In the mentioned equations  $\sigma_I$  and  $\sigma_2$  are variable factors which should be selected according to the desired  $di_d/dt$  and  $dV_{ds}/dt$  rates respectively with considering the limitations presente in (4) and (8). For turn-on condition the modified  $V_g$  has been limited by  $V_{gs,th}$  and for turn-off condition it has been limited by zero. Accordingly, smaller  $\Delta V_m$  has higher impact on the switching transient and oscillations suppression.

#### 2.3. Controller Tuning

According to the presented method, the level of applied intermediate voltages and their time duration should be determined. The influence of each control parameter on the switching transient behaviour is explained here. Also, the optimal interval values for each switching condition should be determined.

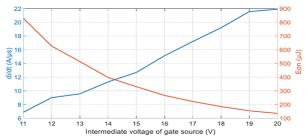

## 2.3.1. Tuning for turn-on

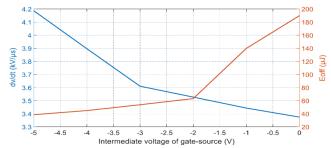

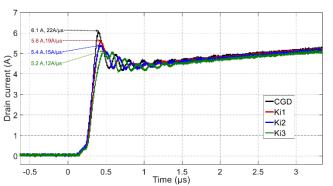

Based on what expressed in previous section, Ki coefficient determines the level of intermediate voltage which can be reduced up to MOSFET's threshold voltage. As a result, the applied intermediate voltage affects to did/dt and current overshoot at turn-on. The time duration of intermediate voltage is another consideration that must be long enough to cover turn-on active region. In this case study, 3 µs has been considered for Di. In order to realize which level of reduced gate voltage provides a desirable did/dt and current overshoot, the corresponding MOSFET is tested by different intermediate voltage values. Fig. 4 shows the effect of controller on MOSFET behaviour at turn-on.

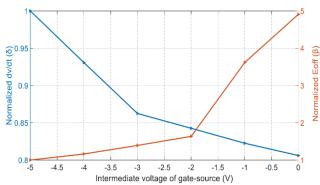

#### 2.3.2. Tuning for turn-off

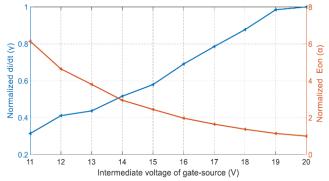

Also, the voltage transition (dv/dt) and overshoot  $(V_{DS\text{-}peak})$  are being affected by intermediate voltage while turn off condition (according to (3)). The resultant intermediate gate voltage through  $K_{\nu}$  and its consequence on MOSFET behaviour at turn-off has been reflected in Fig. 5. In this controlling stage,  $D_{\nu}$  is 2  $\mu$ s which covers whole transient behaviour of MOSFET while turn-off with considering worst case.

## 3. TEST CONDITION

Experimental tests evaluate the performance of the proposed gate driver. The test circuit is a standard clampedinductive circuit which is depicted in Fig. 1. The driving power SiC MOSFET and the clamped SiC MOSFET both are from a same type (SCT2080KE). The parasitic inductance (LS) which comes from the loop of the PCB and power devices is 120 nH. The load current is 6 A, and the value of L in load is 330 µH. A square signal with 50% of duty cycle and frequency at 100 kHz has been applied to the input. The voltage of dc-bus is 400 V and the  $V_{gg}$  supply for original gate driver is -5/+18 V. The applied gate resistor ( $R_g$ ) for turningon is 33 ohms and for turning-off is 46 ohms. The experimental waveforms have been captured by a Tektronix MSO 4054 (500 MHz) digital oscilloscope. The insulators and the safety instruments for protection are not demonstrated here.

## 3.1. Optimized Tuning

The product of multiplication of the drain-source voltage  $V_{dsi}(t)$  to output current  $I_d(t)$  during the switching time results

**Fig. 4:** The effect of intermediate gate-voltage levels on the peak value of current transient and  $di_d/dt$  while turn-on control domain.

**Fig. 5:** The effect of intermediate gate-voltage levels on voltage transition and voltage overshoot in turn-off control domain.

corresponding switching loss. The lost energy while turn-on and turn-off can be calculated from (12) and (13), respectively. Accordingly, to reach an optimized design, the effect of  $K_i$  and  $K_v$  on switching loss and peak value of oscillations are evaluated.

$$E_{on} = \int_{t_0}^{t_5} v_{ds(t)} \times i_{d(t)} dt$$

(12)

$$E_{off} = \int_{t_{e}}^{t_{9}} v_{ds(t)} \times i_{d(t)} dt$$

(13)

First, each one of the switching losses and peak values of current transient (at turn-on) and voltage overshoot (at turnoff) must be normalized as below equations.

$$\alpha = \frac{E_{on}}{E_{min,on}} \tag{14}$$

$$\beta = \frac{E_{off}}{E_{min.off}} \tag{15}$$

In this analysis, the minimum value of switching loss  $(E_{min})$  is assumed when the minimum possible value of  $R_g$  has been used. This value for each switching condition is 6.3  $\Omega$ . Also, in this condition the maximum peak value of current transient  $(i_{d,max,peak})$  and maximum voltage overshoot  $(V_{ds,max,ov})$  can be measured.

$$\gamma = \frac{di_d/dt}{d_{id}/dt - max} \tag{16}$$

$$\delta = \frac{dv_{ds}/dt}{dv_{ds}/dt - max} \tag{17}$$

$\alpha$  and  $\gamma$  present the normalized values of the lost energy and peak value of current oscillations at turn-on condition respectively. Also,  $\beta$  and  $\delta$  represent the normalized values of the lost energy and voltage overshoot at turn-off condition

respectively. With these assumptions, the optimal intermediate gate voltages for each switching state can be obtained. Fig. 6 and Fig. 7 show these optimal intermediate gate-source voltages.

To realize the effect of  $V_{GS}$  value on the transient behaviour of switch while turning-on equation (18) represents the relation of current peak normalized value (see (16)) to the normalized value of lost energy (see (14)) for a specific VGS value at turn-on condition. Also, in the same way it can be realized for turning-off condition by (19).

The test results base on (18) have been reflected in Table 1 and for turn-off condition have been reflected in Table 2. Then, the highest value of  $\gamma/\alpha$  column expresses the highest impact of  $V_{GS}$  value or in other word it belongs to optimum value of  $V_{GS}$ .

$$V_{Gs_{on}} = \left| \frac{\gamma_n}{\alpha_n} \right|_{max} \tag{18}$$

$$V_{Gs_{off}} = \left| \frac{\delta i}{\beta i} \right|_{max} \tag{19}$$

**Fig. 6:** Optimal intermediate voltage for gate-source (*V*) at turn-on.

**Fig. 7:** Optimal intermediate voltage for gate-source (V) at turn-off.

Table 3 shows the optimal setting at both switching states and corresponding values. Through original GD, SiC MOSFET has been driving with  $V_g$ = +20/-5 V and the implemented external gate resistor ( $R_g$ ) is valid for the new GD as well. Though defined coefficients, Ki delivers  $V_{D+}$  = 18V to the gate for switching-on and by  $K_v$  it gets  $V_{D-}$  = -4V while turn-off state.

## 4. EXPERIMENTAL VALIDATION

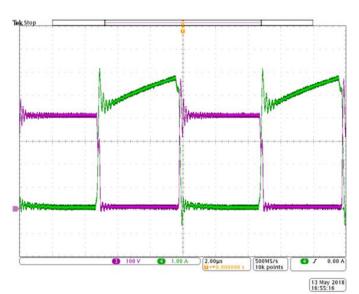

The proposed GD is validated by experimental tests. In order to evaluate the performance of new GD, the transient behaviour of the MOSFET in both with original GD and with proposed GD are compared with together.

#### 4.1. The Test Results

The profile of output parameters ( $i_d$  and  $V_{DS}$ ) of MOSFET when it is driven by original GD are demonstrated in Fig. 8. Then in next figure, for a closer look, the switching behaviour of MOSFET driven by new GD is zoomed in different tuning conditions.

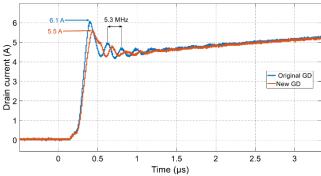

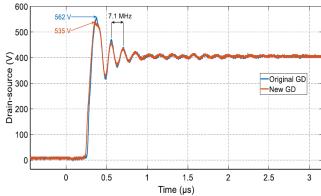

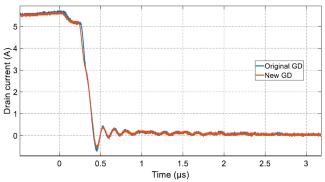

As can be seen in Fig. 9, the overshoot value in output current and corresponding oscillations can be suppressed by applying different  $K_i$ . The biggest suppression rate belongs to which has smallest  $\Delta V_{ml}$  (see (6) and Fig. 3). However, the optimized value ( $V_{D+} = 18\text{V}$  and  $V_{D-} = -4\text{V}$ ) for driving is compared with original gate driver. Fig. 10 and Fig. 11 represent the  $i_d$  current waveform while turning on and off conditions.

Although the proposed GD may suppresses the overshoot up to 5.2 A, however, the optimized tuning condition the overshoot can be reduced up to 5.5 A. In this tuning condition,

Table 1: Optimal VGS value in turn-on condition.

| n | $V_{GS}$ | γ       | $\alpha$ | $\gamma/\alpha$ |

|---|----------|---------|----------|-----------------|

| 1 | 19       | 0.0155  | 0.141    | 0.1099          |

| 2 | 18       | 0.01078 | 0.229    | 0.4707          |

| 3 | 17       | 0.0913  | 0.274    | 0.3332          |

| 4 | 16       | 0.095   | 0.326    | 0.2914          |

| 5 | 15       | 0.111   | 0.474    | 0.2341          |

| 6 | 14       | 0.063   | 0.497    | 0.1267          |

**Table 2:** Optimal VGS value in turn-off condition.

| i | $V_{GS}$ | ν      | α     | ν/α    |

|---|----------|--------|-------|--------|

| 1 | -4       | 0.0693 | 0.163 | 0.425  |

| 2 | -3       | 0.0683 | 0.23  | 0.297  |

| 3 | -2       | 0.0198 | 0.243 | 0.0815 |

**Table 3:** The controller tuning parameters

| Table 5. The conditioner tuning parameters. |           |       |   |       |                 |                  |                  |              |                 |

|---------------------------------------------|-----------|-------|---|-------|-----------------|------------------|------------------|--------------|-----------------|

|                                             | P         | Value | P | Value | $E_{on}(\mu J)$ | $E_{off}(\mu J)$ | $E_{min}(\mu J)$ | id, $max(A)$ | Vds, max, or(V) |

| Tauma                                       | $K_i$     | 0.122 | α | 1.52  | 190             |                  | 125              | 6.6          |                 |

| Turn - on                                   | $D_i$     | 3 μs  | γ | 0.86  | - 190           | -                | 123              | 6.6          | =               |

| Tauma of f                                  | $K_{\nu}$ | 0.1   | β | 1.18  |                 | 46               | 39               |              | 580             |

| Turn-off                                    | $D_{v}$   | 2 μs  | δ | 0.93  |                 | 40               | 39               | -            | 300             |

**Fig. 8:** Output voltage and current of MOSFET driven by original GD.

**Fig. 9:** Zoomed view of drain current with different  $K_i$ .

**Fig. 10:** Drain current with new GD (optimal tuning value) and original GD at turning-on.

**Fig. 11:** Drain current with new GD (optimal tuning value) and original GD at turning-off.

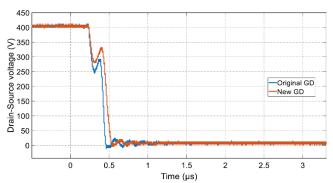

**Fig. 12:** Drain-Source voltage with new GD (optimal tuning value) and original GD at turning-on.

**Fig. 13:** Drain-Source voltage with new GD (optimal tuning value) and original GD at turning-off.

the slope of the current  $(di_d/dt)$  in fundamental frequency (100 KHz) ten times has been increased compare to its maximum value. Also the current fluctuation in switching-on condition with 5.3 MHz (see Fig. 10) highly has been removed which both manners help to eliminate EMI problem from switch mode power supplies.

This comparison can be carried out in the case of drain-source voltage as well. Fig. 12 and Fig. 13 demonstrate the output voltage profiles with original and new GDs in both switching condition.

The obtained results show that output voltage at turn-off condition gets minimum effect from applied control method.

## 4.2. Performance Index

Based on previous subsection, the experimental setup of the gate driver for both switching states has developed. In order to observe the effect of the applied GD, an analytical test between new GD and original GD (with minimum  $R_{g,ext}$ values) has been carried out. The purpose of this comparison is the evaluation of transient behaviour during the operation of new GD and the CGD. Another criteria in this analysis is the comparison of the switching losses between these GDs. The change of gate resistor ( $R_{g,ext}$ ) is known as a conventional driver for MOS-channel switches [27-28]. So, as a conventional solution,  $R_{g,ext}$  is increased up to 15  $\Omega$  (for turning on) and 22  $\Omega$  (for turning off) to achieve the same level of overshoot suppression in current and voltage that new GD presents in its operation. In this condition the switching losses of both GDs can be calculated according to (12) and (13). The results have reflected in Table 4.

**Table 4:** The performance index.

| Gate driver                                                 | $I_d$ (A) overshoot | Voltage<br>overshoot (V) | $E_{on}\left( \mu J\right)$ | $E_{off}\left( \mathrm{\mu J}\right)$ | $di_d/dt$ (A/ $\mu$ s) | $dv_{ds}/dt$ (KV/ $\mu$ s) |

|-------------------------------------------------------------|---------------------|--------------------------|-----------------------------|---------------------------------------|------------------------|----------------------------|

| Original gate driver                                        | 6.1                 | 562                      | 125                         | 39                                    | 22                     | 4.2                        |

| New gate driver                                             | 5.5                 | 535                      | 190                         | 46                                    | 19.2                   | 3.9                        |

| CGD,<br>$R_{g,on}$ =15 $\Omega$<br>$R_{g,off}$ =22 $\Omega$ | 5.5                 | 535                      | 212                         | 50                                    | 18.5                   | 3.6                        |

#### 5. CONCLUSION

Based on the obtained results, the new active voltage gate driver has improved transient behavior of the SiC MOSFET in both switching condition. Although this technique mostly improves the switching in turn-on condition, however it has better performance compared to CGD. In this study, we tried to use an optimized gate drive for switching in both switching states. Applying the proposed feedforward controller on SiC technology MOSFETs, optimal tuning of active voltage GD and evaluation of this GD by performance index were the important topics of this study.

## **ACKNOWLEDGMENTS**

This work was supported by the Generalitat de Catalunya, grant number SGR 2017 SGR 967.

## CREDIT AUTHORSHIP CONTRIBUTION STATEMENT

Hamidreza Ghorbani: Conceptualization, Data curation, Formal analysis, Funding acquisition, Investigation, Methodology, Software, Validation, Visualization, Writing - original draft. Jose Luis Romeral Martinez: Conceptualization, Supervision, Validation, Writing - review & editing.

## **DECLARATION OF COMPETING INTEREST**

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper. The ethical issues; including plagiarism, informed consent, misconduct, data fabrication and/or falsification, double publication and/or submission, redundancy has been completely observed by the authors.

#### REFERENCES

- [1] A. Niwa, T. Imazawa, T. Kimur, T. Sasaya, T. Isobe, and H. Tadano, "Novel dead time controlled gate driver using the current sensor of SiC-MOSFET," in *IECON* 2015 - 41st Annual Conference of the *IEEE Industrial* Electronics Society, 2015, pp. 001651 – 001656.

- [2] J. Millan, P. Godignon, X. Perpina, A. Perez-Tomas, and J. Rebollo, "A survey of wide-bandgap power semiconductor devices," *IEEE Trans. Power Electron.*, vol. 29, no. 5, pp. 2155-2163, 2014.

- [3] F. Mo, J. Furuta, and K. Kobayashi, "A low Surge voltage and fast speed gate driver for SiC MOSFET with switched capacitor circuit," in 2016 IEEE 4th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), 2016, pp. 282 285.

- [4] Y. Lobsiger, and J. W. Kolar, "Closed-loop di/dt and dv/dt IGBT gate driver", *IEEE Trans. Power Electronic*, vol. 30, no. 6, pp. 3402 3417, 2015.

- [5] Z. Wang, X. Shi, M.L. Tolbert, F. Wang, and B.J. Blalock "A di/dt feedback-based active gate driver for smart switching and fast overcurrent protection of IGBT modules", *IEEE Trans. Power Electronics*, vol. 29, no. 7, pp. 3720 3732, 2014.

- [6] Y. Lobsiger, and J. W. Kolar, "Closed-loop di/dt and dv/dt control and dead time minimization of IGBTs in bridge leg configuration", in 2013 IEEE 14th Workshop on Control and Modeling for Power Electronics (COMPEL), 2013.

- [7] H. Ghorbani, V. Sala, A. Paredes, and L. Romeral, "Embedding a feedforward controller into the IGBT gate driver for turn-on transient improvement" *Microelectronics Reliability*, vol. 80, pp. 230 240, 2018.

- [8] L. Shu, J. Zhang, F.Z. Peng, and Z. Chen, "A voltage controlled current source gate drive method for IGBT devices," in *Proc. of IEEE Energy Conversion Congr. and Expo. (ECCE)*, 2014.

- [9] S. Yin, K. J Tseng, R. Simanjorang, and P. Tu, "Experimental comparison of high-speed gate driver design for 1.2-kV/120-A Si IGBT and SiC MOSFET modules", *IET Power Electronics*, vol. 10, no. 9, pp-979 – 986, 2017.

- [10] J. Wang, H. S. h. Chung, and R. T. h. Li, "Characterization and experimental assessment of the effects of parasitic elements on the MOSFET switching performance," *IEEE Trans. Power Electron.*, vol. 28, no. 1, pp. 573–590, 2013.

- [11] Y. Lobsiger, and J. W. Kolar, "Closed-loop di/dt and dv/dt IGBT gate driver", *IEEE Trans. Power Electronic*, Vol. 30, no. 6, pp. 3402 3417, June. 2015.

- [12] P. Nayak, K. Hatua "Active gate driving technique for a 1200 V SiC MOSFET to minimize detrimental effects of parasitic inductance in the converter layout", *IEEE Trans. Industry Appl.*, vol. 54, no. 2, pp. 1622-1633, 2018.

- [13] H. G. Lee, Y. H. Lee, B. S. Suh, and D. S. Hyun, "An improved gate control scheme for snubberless operation of high power IGBTs," in 1997 Thirty-Second IAS Annual Meeting Industry Applications Conference, 1997, pp. 975- 982.

- [14] S. Jahdi, O. Alatise, J. A. O. Gonzalez, R. Bonyadi, L. Ran, and P. Mawby, "Temperature and switching rate

- dependence of crosstalk in Si-IGBT and SiC power modules," *IEEE Trans. Ind. Electron.*, vol. 63, no. 2, pp. 849-863, 2016.

- [15] D. W. Peters, "Turn-On Delay Time of MOS Transistors", *Proceedings of the IEEE*, vol. 56, no. 1, pp. 89 90, 1968.

- [16] N. Oswald, P. Anthony, N. McNeill, and B. H. Stark, "An experimental investigation of the trade-off between switching losses and EMI generation with hard-switched all-Si, Si-SiC, and all-SiC device combinations," *IEEE Trans. Power Electron.*, vol. 29, no. 5, pp. 2393–2407, 2014.

- [17] X. Gong, and J. A. Ferreira, "Investigation of conducted EMI in SiC JFET inverters using separated heat sinks," *IEEE Trans. Ind. Electron.*, vol. 61, no. 1, pp. 115–125, 2014.

- [18] P. R. Palmer; J. Zhang, and X. Zhang, "SiC MOSFETs connected in series with active voltage control," in 2015 IEEE 3rd Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Blacksburg, VA, USA, 2015, pp. 60-65.

- [19] L. Shu, J. Zhang, F. Peng, and Z, Chen, "An active current source IGBT gate drive with closed-loop di/dt and dv/dt control" *IEEE Trans. Power Electron.*, vol. 32, no. 5, pp. 3787 3796, 2017.

- [20] H. Fujita, "A resonant gate-drive circuit capable of high-frequency and high-efficiency operation," *IEEE Trans. Power Electron.*, vol. 25, no. 4, pp. 962–969, 2010.

- [21] D. Peftitsis, and J. Rabkowski, "Gate and base drivers for silicon carbide power transistors: An overview," *IEEE Trans. Power Electron.*, vol. 31, no. 10, pp. 7194–7213, 2016.

- [22] K. Yamaguchi, Y. Sasaki, and T. Imakubo, "Low loss and low noise gate driver for SiC-MOSFET with gate

- boost circuit," in *IECON 2014-40th Annual Conference* of the *IEEE Ind. Electron. Soc.*, pp. 1594-1598.

- [23] Z. Wang, X. Shi, M.L. Tolbert, F. Wang, and B.J. Blalock "A di/dt feedback-based active gate driver for smart switching and fast overcurrent protection of IGBT modules", *IEEE Trans. Power Electronics*, vol. 29, no. 7, pp. 3720 3732, 2014.

- [24] H. Riazmontazer, and S. K. Mazumder, "Optically switched-drive-based unified independent dv/dt and di/dt control for turn-off transition of power MOSFETs," *IEEE Trans. Power Electron.*, vol. 30, no. 4, pp. 2338–2349, 2015.

- [25] H. Riazmontazer, A. Rahnamaee, A. Mojab, S. Mehrnami, S. K. Mazumder, and M. Zefran, "Closed-loop control of switching transition of SiC MOSFETs," in 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), pp. 782–788, 2015.

- [26] Fink. K, and S. Bernet, "Advanced Gate Drive Unit With Closed-Loop dic/dt Control", *IEEE Trans. Power Electronics*, vol. 28, no. 5, pp. 2587 2595, 2013.

- [27] A. Paredes, V. Sala, H. Ghorbani, and L. Romeral, "A novel active gate driver for improving SiC MOSFET switching trajectory", *IEEE Trans. Ind. Electron.*, vol. 64, no. 11, pp. 9032-90422, 2017.

- [28] A. Paredes, V. Sala, H. Ghorbani, and L. Romeral, "A novel active gate driver for silicon carbide MOSFET", in *Annual Conference of the IEEE Industrial Electronics Society IECON*, 2016, pp. 3172-3177.

- [29] J. D. Kagerbauer, and T. M. Jahns, "Development of an active dv/dt control algorithm for reducing inverter conducted EMI with minimal impact on switching losses," in 2007 IEEE Power Electronics Specialists Conference, Orlando, FL, USA, 2007, pp. 894-900.

#### Copyrights

© 2023 Licensee Shahid Chamran University of Ahvaz, Ahvaz, Iran. This article is an open-access article distributed under the terms and conditions of the Creative Commons Attribution –Non-Commercial 4.0 International (CC BY-NC 4.0) License (http://creativecommons.org/licenses/by-nc/4.0/).